交错的马刺:时间不匹配的数学

我们已经使用我们精美的数学家帽来查看偏移和增益不匹配的杂散幅度,所以现在让我们使用它来量化由于时序不匹配而导致的杂散电平。正如我们在前面的讨论中看到的,由于时序失配而产生的杂散出现在 fS/2 ± f 处,这与增益失配杂散出现的位置相同。

现在,我们的讨论结果将为我们留下信息,这将告诉我们f处有多少刺激。 S/2 ± f 是增益不匹配的结果,也是时序不匹配的结果。这很重要,因为它将帮助我们判断哪种不匹配在交错时给我们带来了最大的麻烦。希望我们最终不会陷入两者都非常糟糕的情况......但这不是首先尝试交织的重点。我们希望从设计过程一开始就最大限度地减少不匹配。

因此,让我们戴上数学家帽子,再次深入研究数学,看看我们如何计算 f 处的支线大小。 S/2 ± f 由于时序不匹配。我想我们要把这顶帽子暂时放下,重新戴上我们的工程师帽子,但让我们再戴上我们的数学帽子一段时间。

现在让我们看一下计算结果,看看刺激措施的时间错配有多大。让我们看看下面的公式 1,其中 ω a 是 模拟 输入频率,ΔτE 是时序失配。

现在,我们来考虑双通道器件中两个 14 位 250MSPS ADC 之间的典型时序不匹配。典型值可能约为 1ps。

1ps 的时序不匹配将导致 f 处出现 70dBcS/2 ± f 的交错杂散。这对于大多数应用可以容忍的最大杂散电平来说是正确的。这仍然很容易主导交错式 ADC 的无杂散动态范围 (SFDR) 规格。

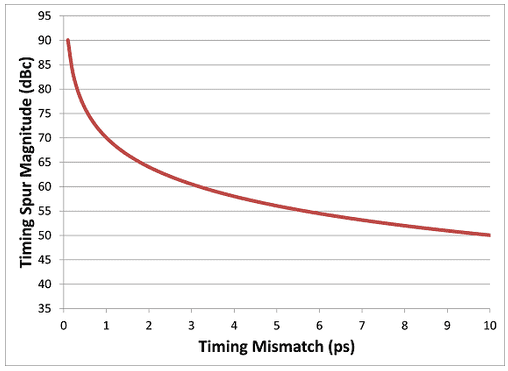

二次和三次谐波以及任何其他杂散输出可能低于 70dBc。现在让我们看看如何才能超过 70dBc 水平。我们希望降低它,因为某些应用需要 80 至 90dBc 的无杂散动态范围。在下面的图 1 中,绘制了时序失配杂散的幅度与时序失配(以皮秒为单位)的关系。

图1

时序杂散和时序不匹配(交错式 14 位 ADC)。

这个情节向我们展示了几件事。与增益失配图类似,杂散的幅度大致遵循指数衰减,一旦失配接近 10ps,杂散幅度图就几乎变得平坦。此外,它告诉我们需要使定时失配非常小(飞秒范围)才能使杂散幅度达到 90dBc 范围。这让我们了解两个 ADC 之间的时序需要如何匹配。当我们谈论飞秒时,它非常小!

然而,随着工艺技术的缩小和匹配技术的改进,最大限度地减少交错 ADC 之间的时序失配变得更加容易。请注意,布局只是拼图的一小部分。目前 ADC 达到的高速达到了千兆位采样范围,因此需要某种校准来减少飞秒范围的时序失配。这告诉我们,还有希望;我们只需要找出一个好的校准方案来减少失配。

审稿编辑:郭婷

-->相关文章

- 11-28 强的新纪元:深度融合与改变我们的世界

- 11-28 智能家居行业趋势如何,趋势:引领行业标准化

- 11-28 笔记本市场前景展望:竞争格局、发展趋势与营销策略

- 11-27 5G手机性价比排行榜最新出炉!这些机型值得购买!

- 11-27 流媒体服务的优缺点,让你畅享视听盛宴

- 11-27 数码摄影摄像入门全攻略:从设备到后期,一篇文章教你

- 11-26 5G手机评测排名前十:让你拥有最快的网速!

- 11-26 最新5g手机评测排行榜前十名,手机评测排行榜前十名

- 11-26 电子书阅读器大比拼:谁是最亮的星?

- 11-25 无人机摄影:飞越天际,捕捉绝美瞬间

- 11-25 智能家居趋势如何描述,生活的潮流与变革

- 11-25 主流电子书阅读器评测,让你选出最适合自己的阅读利器

- 11-24 虚拟现实和增强现实:技术差异与未来融合

- 11-24 智能家居以后的趋势,未来已来,智能家居引领潮流

- 11-24 虚拟现实技术国家重点实验室,重点实验室:开启未来科

- 11-23 5G手机大对比:优缺点一览,让你选购无忧

- 11-23 掌握数码相机与摄影技巧,拍出绝美照片

- 11-23 笔记本电脑市场分析表格

- 11-22 数码相机技术美:捕捉精彩画面的奥秘

- 11-22 掌握数码相机与摄影技巧,拍出惊艳作品!

- 最近发表